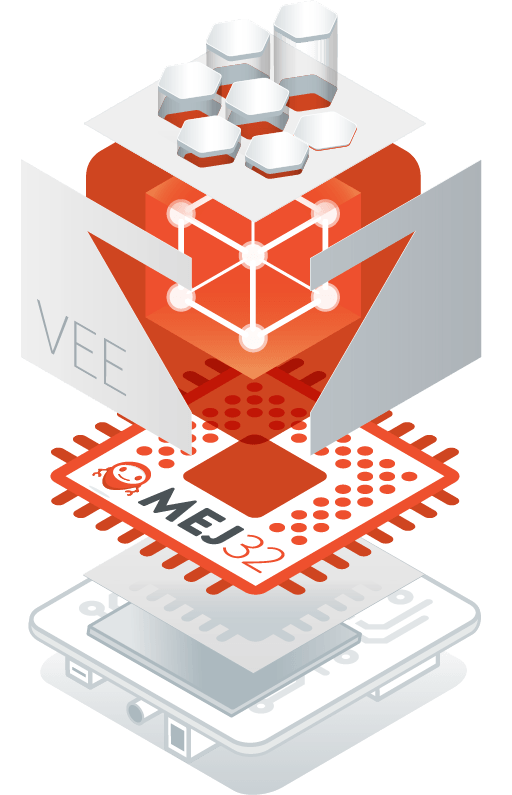

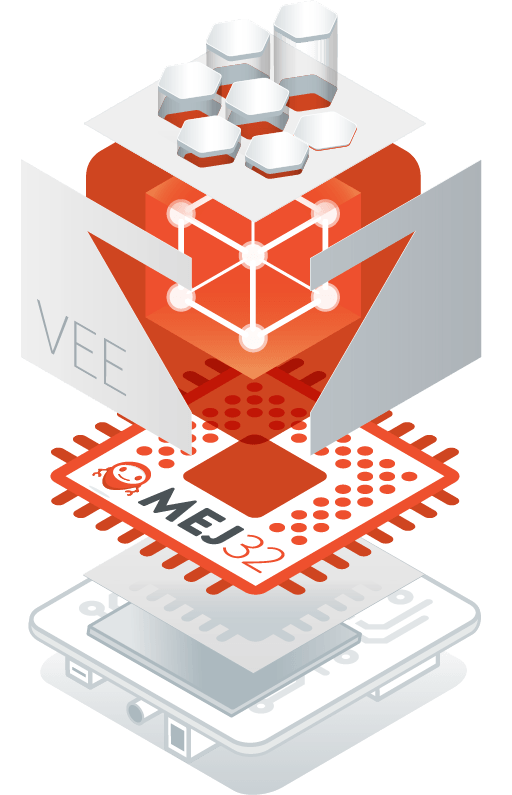

When provided in software, MEJ32 is a 32-bit virtual core optimized for various embedded systems processors including ARM Cortex-M, ARM Cortex-A, Renesas RX and V850, MIPS32, Infineon TriCore, and Tensilica Xtensa. When provided in hardware, it is a regular core IP, qualified as a VPU.

MEJ32 provides a unique Instruction Set Architecture (ISA). A tool, named SOAR, generates MEJ32 ISA code in ELF format, out of both the binary j2vm-v7 ISA code format, and the binary wasm-R2.0 code format. The SOAR also acts as a linker.

For hardware version of the MEJ32 core, please contact MicroEJ for availability.

MicroEJ offers MICROEJ MEJ32 implementations for a wide range of popular hardware architectures. Examples of MICROEJ VEE are available for dedicated evaluation boards.

Follow the link below in order to find out if your hardware is supported and which MICROEJ VEE implementation is right for your project according to your processor core architecture and C tool chain.